기록 차원에서 남겨둡니다.

STM32F103xC 를 사용했는데 PWM 시그널이 2가지가 필요했습니다.

그런데 TIM3 CH4에서 TIM8 데이터가 나옵니다.

칩 불량인가? 다른 칩에서도 같은 문제가 나오네요.

이 문제로 많은 시간을 허비하며 문제점 파악에 나섰고,

TIM 내부 블럭도와 CubeIDE 에서 실마리를 발견했습니다.

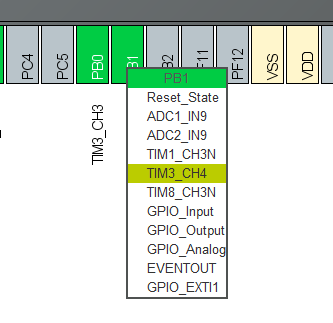

문제가 발생한 PWM Pin 을 살펴보는중 Remap 사용시 TIM8 CH3N 을 발견했습니다.

이 N은 뭐하는 걸까?

PWM 신호를 RS485와 같이 미러신호가 필요할 경우가 있을껍니다. 아니면 똑같은 시그널을요.

어쨌든 PWM 시그널을 다른 포트로 내보낼 수 있습니다. 즉 GPIOC 를 사용하는 TIM8 에서 GPIOB 로 TIM6를 ㅁ

아무튼 코드에서 붉은색 부분이 문제였습니다.

TIM_OCInitTypeDef TIM_OCInitStructure;

TIM_OCInitStructure.TIM_OCMode = TIM_OCMode_PWM1;

TIM_OCInitStructure.TIM_OutputState = TIM_OutputState_Enable;

TIM_OCInitStructure.TIM_OutputNState = TIM_OutputNState_Enable;

TIM_OCInitStructure.TIM_OCPolarity = TIM_OCPolarity_High;

TIM_OCInitStructure.TIM_OCNPolarity = TIM_OCNPolarity_Low;

TIM_OCInitStructure.TIM_OCIdleState = TIM_OCIdleState_Set;

TIM_OCInitStructure.TIM_OCNIdleState = TIM_OCIdleState_Reset;

TIM_OCInitStructure.TIM_Pulse = 0;

TIM_OC3Init(TIM8, &TIM_OCInitStructure);

정리하면 타이머 블록을 보면 신호가 분기되어 2곳으로 내보낼수 있습니다.

출력 여부를 결정하는 TIM_OutputState, TIM_OutputNState 의 값을 반드시 지정해야 합니다.

특히 구조체변수 TIM_OCInitStructure 선언시 기본 값이 셋팅되는 것이 아니므로 꼭! 설정값 여부를 지정해야 합니다.

TIM_OCInitStructure.TIM_OutputNState = TIM_OutputNState_Disable;

이렇게 해주면 TIM3의 CH4 와 TIM8의 CH3N 의 충돌이 해결됩니다.

굿밤~!